���] �ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��):������Ӌ(j��)��(HPC)��ϵ�y(t��ng)��(j��)���b(SIP)

-

>

��·܇����(ZINN�Ĺ�·܇�S���c���B(y��ng)�ؼ�)

-

>

���w���·�O(sh��)Ӌ(j��)(��)

-

>

���ڂ�(g��)�Ի��O(sh��)Ӌ(j��)���Ե����ܽ�ͨϵ�y(t��ng)�P(gu��n)�I���g(sh��)

-

>

���Ӱٳ�:�F���ٔ�(sh��)����D����ɫ

-

>

ɽ�|��������������˾���g(sh��)�D(zhu��n)���c���g(sh��)��(chu��ng)�vʷ�����Ї�(gu��)�ߵȼ��g(sh��)�������K��(1949��1961)�Ա����^(q��)������

-

>

�F·�C(j��)܇��Ҫ.��������(d��ng)��(n��i)ȼ.����C(j��)܇

-

>

���S̹�ĵ�������:���ڬF(xi��n)�������܌W(xu��)�Ć��}�c�}�j(lu��)

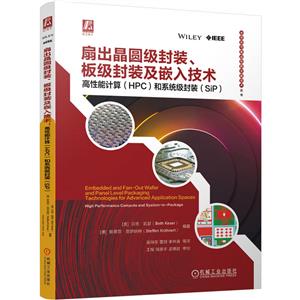

�ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��):������Ӌ(j��)��(HPC)��ϵ�y(t��ng)��(j��)���b(SIP) ���(qu��n)��Ϣ

- ISBN��9787111755807

- �l�δa��9787111755807 ; 978-7-111-75580-7

- �b����ƽ�b-�zӆ

- ��(c��)��(sh��)�����o(w��)

- ���������o(w��)

- ���ٷ��>>

�ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��):������Ӌ(j��)��(HPC)��ϵ�y(t��ng)��(j��)���b(SIP) ������ɫ

1.���x�Ըߡ�������ȫ��ӡˢ����������֪��оƬ�a(ch��n)Ʒ�D��

2.��(n��i)�ݺá��������а������O���ֱ���оƬ�������ֱ�оƬ���_(t��i)�e늵�оƬ�����¹��оƬ�IJ�ɫ�DƬ���������ҷքeՓ�����������Եļ��g(sh��)·���ͼ��g(sh��)���c(di��n)������߀�Դ˽�B��Ŀǰ�����ĺ����ڰl(f��)չ��оƬ���b���g(sh��)�ļ��g(sh��)��(du��)�ȡ��ɱ���(du��)�ȣ��dz����Ѕ����r(ji��)ֵ��

3.���ߏ�(qi��ng)����������ԭ����ؐ˼�LJ�(gu��)�H��ӽM�b�c���b�f(xi��)��(hu��)��IMAPS����ԭ��(zh��)����ϯ���LJ�(gu��)�H֪���ķ��b���Һ͌W(xu��)�g(sh��)���^�ˡ�

4.�g�ߺá����Ї�(gu��)늿�43�����^���g

�ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��):������Ӌ(j��)��(HPC)��ϵ�y(t��ng)��(j��)���b(SIP) ��(n��i)�ݺ�(ji��n)��

���ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��)��һ����ԭ��(gu��)�H��ӽM�b�c���b�f(xi��)��(hu��)��IMAPS����ϯؐ˼���Pɪ��Beth Keser����ʿ�������Ї�(gu��)늿Ƶ���ʮ���о����M�����g�� ���ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��)���Ķ�Nҕ�nj�(du��)���N�ȳ���Ƕ��ʽоƬ���g(sh��)�M(j��n)���U�������ȏ��Ј�(ch��ng)�ǶȌ�(du��)�ȳ��;��A��(j��)���b�ļ��g(sh��)څ��(sh��)�M(j��n)�з�����Ȼ��ijɱ��ǶȌ�(du��)�@Щ��Q�����M(j��n)���о���ӑՓ�����_(t��i)�e늡�Deca�����¹�ȹ�˾��(chu��ng)����Advanced��(y��ng)���I(l��ng)��ķ��b��͡�����߀�������¼��g(sh��)�ͬF(xi��n)�м��g(sh��)��IP�h(hu��n)���ͳɱ����^��ͨ�^��(du��)���ͷ��b�댧(d��o)�wIDM��˾����Ӣ�ؠ��������֡����ǵȣ��ļ��g(sh��)�_�l(f��)�ͽ�Q�����ķ������U���˸�댧(d��o)�w�����S������S�İ댧(d��o)�w����*��(du��)�W(xu��)�g(sh��)���ǰ���о��M(j��n)չ�M(j��n)���˚w�{���Y(ji��)��

�ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��):������Ӌ(j��)��(HPC)��ϵ�y(t��ng)��(j��)���b(SIP) Ŀ�

������

�g����

ԭ�����x

ԭ��ǰ��

��1�� �ȳ����A��(j��)�Ͱ弉(j��)���b���Ј�(ch��ng)�ͼ��g(sh��)څ��(sh��)

1.1 �ȳ����b��(ji��n)��

1.1.1 �vʷ����

1.1.2 �P(gu��n)�I�(q��)��(d��ng)������ʲô���ȳ����b

1.1.3 �ȳ����A��(j��)���b��FO-WLP���c�ȳ��弉(j��)���b��FO-PLP��

1.1.4 ����(g��u)���ɵ��ȳ����b�l(f��)չڅ��(sh��)

1.2 �Ј�(ch��ng)�śr�͑�(y��ng)��

1.2.1�ȳ����b���x

1.2.2 �Ј�(ch��ng)���֣�Core FO��HD FO �� UHD FO�Č�(du��)��

1.2.3 �Ј�(ch��ng)�r(ji��)ֵ��������N���A(y��)�y(c��)

1.2.4 ��(d��ng)ǰ��δ��(l��i)��Ŀ��(bi��o)�Ј�(ch��ng)

1.2.5 �ȳ����b�đ�(y��ng)��

1.3 ���g(sh��)څ��(sh��)����(y��ng)�

1.3.1 �ȳ����b���g(sh��)·���D

1.3.2 �����̵��ȳ����b���g(sh��)

1.3.3 ����(y��ng)朸���

1.3.4 ��(d��ng)ǰ�Ĺ���(y��ng)朄�(d��ng)�B(t��i)����

1.4�ȳ��弉(j��)���b(FO-PLP)

1.4.1 FO-PLP���(q��)��(d��ng)�������R������(zh��n)

1.4.2 FO-PLP���Ј�(ch��ng)�͑�(y��ng)��

1.4.3 FO-PLP����(y��ng)�̸���

1.5ϵ�y(t��ng)�O(sh��)����

1.5.1 �����ȳ����b�ĽK��ϵ�y(t��ng)���D

1.5.2 ���_(d��)IC��eWLB�cRCP

1.5.3 �ɱ����^

1.6�Y(ji��)Փ

�����īI(xi��n)

��2��FO-WLP���ȳ��;��A��(j��)���b���g(sh��)���c�������g(sh��)�ijɱ����^

2.1��(ji��n)��

2.2���ڻ��(d��ng)�ijɱ�ģ��

2.3 FO-WLP׃���ijɱ�����

2.3.1��ˇ�εijɱ�

2.3.2 FO-WLP�IJ�ͬ��ˇ�N�

2.4 FO-WLP�c�����I�Ϻ͵��bоƬ�ijɱ����^

2.5�ѯBʽ���b(PoP)�ijɱ�����

2.6�Y(ji��)Փ

�����īI(xi��n)

��3�� �ȳ����ɣ�InFO�����g(sh��)���Ƅ�(d��ng)Ӌ(j��)���ϵđ�(y��ng)��

3.1 ����

3.2���A��(j��)������b

3.2.1��늌Ӻ��ٷֲ��ӣ�RDL��

3.2.2 �c(di��n)�½��ٻ� (UBM)

3.2.3 �ɿ����c����(zh��n)

3.2.4 ��оƬWLP

3.3���A��(j��)�ȳ�ϵ�y(t��ng)����

3.3.1 оƬ�����cоƬ����

3.3.2 �ܷ��cƽ̹��

3.3.3 �ٷֲ��ӣ�RDL��

3.3.4 ͨ���c��ֱ���B

3.4 ���ɟo(w��)ԴԪ����IPD��

3.4.1 ��Qֵ�����S�ݾ�Ȧ늸�

3.4.2 �쾀���ɷ��b��AiP����5Gͨ��

3.4.3 ���ں��ײ�ϵ�y(t��ng)���ɵğo(w��)ԴԪ��

3.5 ���ʡ����ܡ����γߴ�ͳɱ�

3.5.1 ��̖(h��o)���Դ������

3.5.2 ɢ��͟�����

3.5.3 ���κͺ��

3.5.4 �Ј�(ch��ng)�����ڳɱ�

3.6 �����Y(ji��)

�����īI(xi��n)

��4�� �����ȳ� ��InFO�� �ڸ�����Ӌ(j��)���еđ�(y��ng)��

4.1 ����

4.2 3D���b��Ƭ�ϼ���ϵ�y(t��ng)��SoIC��

4.3 CoWoS-R, CoWoS-S��CoWoS-L

4.4 InFO-L �� InFO-R

4.5 �����ܶȻ��B��InFO���b��InFO-UHD��

4.6��ѯBϵ�y(t��ng)���� ��MUST�� ��Must-in-Must��MiM��

4.7 ���dInFO���g(sh��)(InFO-oS)�;ֲ��軥�BInFO���g(sh��)(InFO-L)

4.8 ���d�惦(ch��)оƬ��InFO ���g(sh��)(InFO-MS)

4.9 3D���InFO (InFO-3DMS) and CoWoS-L

4.10 ���A��InFOϵ�y(t��ng) (InFO_SoW)

4.11 ���ɰ���ϵ�y(t��ng)��SoIS��

4.12 ����ʽ��(n��i)��Ӌ(j��)�㣨ImMC��

4.13�����Y(ji��)

�����īI(xi��n)

��5�� ���ڸ��ܶȼ��ɵ����m��(y��ng)�D�κ�M-ϵ�м��g(sh��)

5.1 ���g(sh��)����

5.2 ��(y��ng)���c�Ј�(ch��ng)

5.3�������b�Y(ji��)��(g��u)

5.4 ���칤ˇ���̺��������

5.5�O(sh��)Ӌ(j��)���Ժ�ϵ�y(t��ng)��������

5.6 ���m��(y��ng)�D��

5.7�������ͿɔU(ku��)չ��

5.8 ���b����

5.9 �����ԺͿɿ��Ԕ�(sh��)��(j��)

5.10 늜y(c��)ԇע�����(xi��ng)

5.11�����Y(ji��)

�����īI(xi��n)

��6�� ������弉(j��)���b�Į���(g��u)����

6.1����

6.2�ȳ��弉(j��)���b

6.3 �弉(j��)���b�Ľ�(j��ng)��(j��)Ч�����

6.4�����Y(ji��)

�����īI(xi��n)

��7�� ����߹���ģ�K��SiPģ�K����һ��оƬǶ�뼼�g(sh��)

7.1 ���g(sh��)����

7.2���b���A(ch��)�Y(ji��)��(g��u)

7.3��(y��ng)���c�Ј�(ch��ng)��HPC��SiP��

7.4���칤ˇ��BOM

7.5�O(sh��)Ӌ(j��)���c(di��n)

7.6ϵ�y(t��ng)��������

7.7���b����

7.8 �������c�ɿ��Ԕ�(sh��)��(j��)

7.9늜y(c��)ԇ�Ŀ��]����

7.10 �����Y(ji��)

�����īI(xi��n)

��8�� ���M(j��n)�����ϵ�оƬ���ɼ��g(sh��)(����Ƕ��Ϳ�ǻ)

8.1 ����

8.2ͨ�^ʹ��Ƕ��ʽоƬ���b(ECP?)��(sh��)�F(xi��n)����(g��u)����

8.3 Ƕ�빤ˇ

8.4 �����x��

8.5 �O(sh��)Ӌ(j��)���g(sh��)

8.6 �y(c��)ԇ

8.7 ECP���g(sh��)�đ�(y��ng)��

8.8 ����PCB�еĿ�ǻ�M(j��n)�Ю���(g��u)����

8.9 ���b���ܡ���(w��n)���ԺͿɿ���

8.10 �Y(ji��)Փ

�����īI(xi��n)

��9�� ���M(j��n)��Ƕ��ʽ�������塪�� һ�N�`����ȳ����A��(j��)���b���������

9.1 ���g(sh��)��B

9.1.1 C2iM���g(sh��)

9.1.2 C2iM-PLP���g(sh��)

9.2��(y��ng)�ú��Ј�(ch��ng)

9.3���b�Ļ����Y(ji��)��(g��u)

9.3.1 C2iM-PLP���g(sh��)��(j��ng)�(y��n)

9.3.2 C2iM-PLP�c�����I�Ϸ��α�ƽ�o(w��)���_��WB-QFN�����b�͵��bоƬQFN��FC-QFN�����b��ȵă�(y��u)ȱ�c(di��n)

9.3.3 C2iM-PLP�cWLP��FO-WLP��ȵă�(y��u)ȱ�c(di��n)

9.3.4 δ��(l��i)�đ�(y��ng)��

9.3.5 C2iM-PLP�ľ�����

9.4 ���칤ˇ���̼��������

9.5 �O(sh��)Ӌ(j��)Ҏ(gu��)��

9.5.1 ���b�O(sh��)Ӌ(j��)Ҏ(gu��)��

9.5.2 оƬUBM�O(sh��)Ӌ(j��)Ҏ(gu��)��

9.5.3 оƬ�����O(sh��)Ӌ(j��)Ҏ(gu��)��

9.5.4 �~���O(sh��)Ӌ(j��)Ҏ(gu��)��

9.6 ϵ�y(t��ng)��������

9.7 ���a(ch��n)Ҏ(gu��)��Ϳ���չ��

9.8 ���b����

9.8.1 �����

9.8.2 ������

9.9 �����ԺͿɿ��Ԕ�(sh��)��(j��)

9.9.1 ͨ�^��܇�ɿ����J(r��n)�C

9.9.2 ͨ�^�弉(j��)�ɿ����(y��n)�C

9.10 늜y(c��)ԇ��˼��

9.11 �����Y(ji��)

��10�� �����ȳ����A��(j��)���b�����Ի�����

10.1����

10.2���b��*�°l(f��)չڅ��(sh��)

10.3?ʹ��FO-WLP��FHE����FlexTrateTM

10.4?FlexTrateTM�đ�(y��ng)��

���x

�����īI(xi��n)

��11�� ����2.5D��3D����(g��u)���ɵĶ�оƬ�����·���g(sh��)��늺͟��O(sh��)Ӌ(j��)����������

11.1����

11.2 ����(g��u)���Bƴ�Ӽ��g(sh��)��HIST��

11.3 ���ژ�оƬ2.5D���ɼ��g(sh��)�ğ��u(p��ng)��

11.3.1 2.5D��3D�ĵ��ͼܘ�(g��u)

11.3.2 �Ὠģ������

11.3.3 ��ͬ2.5D���ɷ����ğ����܌�(du��)��

11.3.4 2.5D��3D����֮�g�ğ����܌�(du��)��

11.3.5 ���ژ��оƬ2.5D���ɵğ��о�

11.3.6 ��Ƭʽ3D����

11.4 �߹���

�ȳ����A��(j��)���b���弉(j��)���b��Ƕ�뼼�g(sh��):������Ӌ(j��)��(HPC)��ϵ�y(t��ng)��(j��)���b(SIP) ���ߺ�(ji��n)��

ؐ˼���Pɪ��Beth Keser����ʿ������֪���İ댧(d��o)�w���b�I(l��ng)��?q��)��Һ��ИI(y��)�I(l��ng)�䣬��1993��������(gu��)���Π���W(xu��)�@�ò��ϿƌW(xu��)�c���̌W(xu��)ʿ�W(xu��)λ��1997���������Z����W(xu��)��ͼ{-�㙉��У�@�ò�ʿ�W(xu��)λ���Pɪ��ʿ�ڰ댧(d��o)�w�O(sh��)���_�l(f��)������F(xi��n)��ɫ���ѫ@��43�(xi��ng)����(gu��)�����ʹ����������l(f��)��50��ƪ�����������Ħ���_�����w˼�����댧(d��o)�w����ͨ��Ӣ�ؠ���ȫ��댧(d��o)�w��˾���������I(l��ng)��(d��o)���ȳ����A��(j��)���b��FO-WLP�����g(sh��)�_�l(f��)�c�a(ch��n)Ʒ�M���Pɪ��ʿͬ�r(sh��)Ҳ��IEEE Fellow��IEEE��ӷ��b�W(xu��)��(hu��)��EPS���ܳ��v��������2015���(d��n)����ӷ��b��(hu��)�hIEEE EPS ECTC��ϯ��2021�굽2023�꣬��(d��n)�·�(gu��)�H��ӽM�b�c���b�f(xi��)��(hu��)��IMAPS����ϯ����2021�꣬�������ȳ��;��A��(j��)���b�I(l��ng)���ؕ�I(xi��n)���Pɪ��ʿ�@����IEEE EPS���g(sh��)�ɾͪ�(ji��ng)��Ŀǰ�����dz���(chu��ng)��˾Zero ASIC�����켼�g(sh��)�����á�

˹�ٷҡ����_�{�أ�Steffen Kr?hnert���ǵ�(gu��)����˹�D��ESPAT��ԃ��˾�Ŀ��ú̈́�(chu��ng)ʼ�ˡ�IEE EPS��(hu��)�T���ڰ댧(d��o)�w�ИI(y��)�г��^20��Ĺ�����(j��ng)�(y��n)����23��������������ߡ�

- >

��(j��ng)�䳣Մ

- >

������

- >

���wǧ����

- >

�Ї�(gu��)�vʷ��˲�g

- >

�ҏ�δ��˾�����g

- >

�����S�����-�������Ծ���

- >

����?gu��)����x��Ѹ:����Ϧʰ

- >

�ϵ�֮��:���˵��挍(sh��)�ó�

![�]�������đ�(zh��n)��(ch��ng)���P(gu��n)����؛���c�Q(m��o)��](http://image31.bookschina.com/pro-images/250513gs/487100.jpg?id=81)