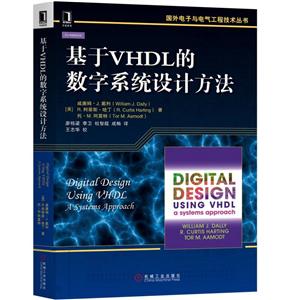

���] ��������c늚�̼��g���������·�OӋ�̳�:VHDLϵ�y���F/WILLIAM JAMES DALLY

-

>

ȫ��Ӌ��C�ȼ���ԇ�����濼�}��ģ�M������Ԕ�⡤����MSOffice������

-

>

�Q���Мy5000�}(���Z�����c���_)

-

>

ܛ�����ܜyԇ.�����c�{�����`֮·

-

>

��һ�д��aAndroid

-

>

JAVA���m����

-

>

EXCEL��̿ƕ�(��ȫ��)(ȫ��ӡˢ)

-

>

��ȌW��

��������c늚�̼��g���������·�OӋ�̳�:VHDLϵ�y���F/WILLIAM JAMES DALLY �����Ϣ

- ISBN��9787111611332

- �l�δa��9787111611332 ; 978-7-111-61133-2

- �b����һ���z�漈

- �Ԕ������o

- ���������o

- ���ٷ��>

��������c늚�̼��g���������·�OӋ�̳�:VHDLϵ�y���F/WILLIAM JAMES DALLY ������ɫ

�m�x��Ⱥ ��˹̹����W ������˹̹����W����Dally���ȸ茣��Harting������炐�ȁ���W����Aamodt������������25�����ϵĽ̌W�����̌��`������ʡ����������������˹̹����W������炐�ȁ���W�����A��W�ȶ�����W�n�̽̌W���á��m�������Ϣ��Ƹ��꼉�W�����о����W�����ּ���ϵ�y�OӋ����Ľ̲ĺͽ̌W���������Լ������ּ���ϵ�y�OӋ�Ĺ��̎���������ʹ�á�

��������c늚�̼��g���������·�OӋ�̳�:VHDLϵ�y���F/WILLIAM JAMES DALLY ���ݺ���

�������锵���·�OӋ���������x���ṩ��һ��ϵ�y����ҕ�ǣ������������⡢�������OӋ����ϵ�y�ṩ�����P�Y�Ϻ��ߡ������ڮ�ǰ���I�电��ϵ�y�OӋ�������Ӳ�������Z�ԣ�VHDL���ͬF��CAD ����ʹ�����P�ļ��ܡ��eע��ϵ�y�����}�������ֽ�̈́��֔���ϵ�y���ӿ��OӋ�ͽӿڕr��Ҳ�漰��Ҫ������������P���}����r������������B��ͬ���ԡ���Ȼ������߀���w�˽M�Ϻ͕r��߉�·���˹��OӋ��

��������c늚�̼��g���������·�OӋ�̳�:VHDLϵ�y���F/WILLIAM JAMES DALLY Ŀ�

����ٝ�u

�g����

ǰ��

���x

���ߺ���

**��������

��1������Ϣ����

1.1������̖

1.2������̖������

1.3������̖��ʾ���s����

1.4����߉����

1.5�����·�cϵ�y��Ӳ�������Z��(VHDL)

1.6ϵ�y�еĔ���߉

���Y

�īI���x

����

��2����ϵ�y�OӋ���`

2.1�OӋ�^��

2.2����ϵ�y��оƬ���·��M��

2.3Ӌ��C�o���OӋ����

2.4Ħ�����ɺ͔���ϵ�y�lչ

���Y

�īI���x

����

�ڶ����ֽM��߉

��3�²�������

3.1ԭ��

3.2����

3.3��ż����

3.4�˜���

3.5�ķ���ʽ��߉�T

3.6Ӳ�������Z���еIJ������_ʽ

���Y

�īI���x

����

��4��CMOS߉�·

4.1�_�P߉

4.2MOS���w�ܵ��_�Pģ��

4.3CMOS�T�·

���Y

�īI���x

����

��5��CMOS�·���ӕr����

5.1CMOS�o�B�ӕr

5.2��ؓ�d�µ����ȳ�

5.3߉Ŭ��������

5.4�ӕrӋ��

5.5�ӕr����

5.6�����ӕr

5.7CMOS�·�Ĺ���

���Y

�īI���x

����

��6�½M��߉�·

6.1�M��߉

6.2�]��

6.3��ֵ����*С헡����c���T�˜���ʽ

6.4���c���·���N���

6.5���Z�D

6.6���b����

6.7�ķ��b�D׃���T

6.8����ȫ��ָ�˺���

6.9���F��֮�e

6.10ð�U

���Y

�īI���x

����

��7�½M��߉�·��VHDL����

7.1���������·��VHDL����

7.2�ؔ��·�Ĝyԇ�ļ�

7.3�߶��g�a��

���Y

�īI���x

����

��8�½M��߉�·������Ԫ

8.1��λ��ӛ

8.2�g�a��

8.3��·������

8.4���a��

8.5�ٲ����̓��Ⱦ��a��

8.6���^��

8.7���

8.8ROM

8.9�x/���惦��

8.10�ɾ���߉���

8.11������

8.12֪�R�a��ģ�K

���Y

�īI���x

����

��9�½M��߉�·�OӋ����

9.1�����·

9.2�����·

9.3���ȼ��ٲ���

9.4�����Α��·

���Y

����

�����������g�\���·

��10�����g�\���·

10.1���M�Ɣ�

10.2���M�Ƽӷ�

10.3ؓ���͜p��

10.4�˷���

10.5����

���Y

����

��11�¶��c�����c��

11.1�`��ı�ʾ���ʶȡ����Ⱥͷֱ���

11.2���c��

11.3���c��

���Y

�īI���x

����

��12�¿����\���·

12.1��ǰ�Mλ

12.2Booth�ؾ��a

12.3�A�Rʿ��

12.4�C��ע�����

���Y

�īI���x

����

��13�����g�\���·�OӋ����

13.1�͔��˷���

13.2���c��ʽ���c��ʽ֮�g���D�Q

13.3FIR�V����

���Y

�īI���x

����

���IJ���ͬ���r��߉

��14�r��߉

14.1�r���·

14.2ͬ���r���·

14.3��ͨ��������

14.4��B����

14.5���ޠ�B�C�Č��F

14.6���ޠ�B�C��VHDL���F

���Y

�īI���x

����

��15�r��s��

15.1�����ӕr����Ⱦ�ӕr

15.2�|�l��

15.3�����r�g�ͱ��֕r�g�s��

15.4�r�ƫ�Ƶ�Ӱ�

15.5�r��ʾ��

15.6�r���߉�C��

���Y

�īI���x

����

��16����ͨ·�ĕr��߉

16.1Ӌ����

16.2��λ�Ĵ���

16.3���ƺ͔�������

���Y

����

��17�·ֽ����ޠ�B�C

17.1�W�����OӋ

17.2��ͨ��̖��������

���Y

����

��18�����a

18.1������a��B�C

18.2ָ������

18.3��·��֧

18.4��Nָ�����

18.5���a�ӳ���

18.6���ε�Ӌ����

���Y

�īI���x

����

��19�r��ʾ��

19.13���lӋ����

19.2SOS�z�y��

19.3�������Α�

19.4�շ������a��/��a��

���Y

�īI���x

����

���岿���`�OӋ

��20����C�͜yԇ

20.1�OӋ��C

20.2�yԇ

���Y

�īI���x

����

��������ϵ�y���OӋ

��21��ϵ�y���OӋ

21.1ϵ�y�OӋ�^��

21.2�OӋҎ��

21.3����

���Y

�īI���x

����

��22�½ӿں�ϵ�y���r��

22.1�ӿڕr��

22.2�ӿڄ��ֺ��x��

22.3���кʹ���ӿ�

22.4ͬ���r��

22.5�r���

22.6�ӿں͕r��ʾ��

���Y

����

��23����ˮ��

23.1��ͨ��ˮ��

23.2��ˮ��ʾ��

23.3��λ�Mλ�ӷ�����ˮ���Y���OӋʾ��

23.4��ˮ��ͣ��

23.5�p�ؾ��_

23.6ؓ�dƽ��

23.7��׃ؓ�d

23.8�YԴ����

���Y

�īI���x

����

��24�»��B

24.1�����B

24.2����

24.3�����_�P

24.4���B�W�j

���Y

�īI���x

����

��25�´惦ϵ�y

25.1�惦��Ԫ

25.2λƬ�ͶѴ惦��

25.3����惦��

25.4���پ���

���Y

�īI���x

����

���߲��֮���߉

��26�®����r���·

26.1��������

26.2�����C�ϣ��|�l�·

26.3�����͠�B�xֵ

���Y

�īI���x

����

��27���|�l��

27.1�i�����Ȳ��Y��

27.2�|�l���ăȲ��Y��

27.3CMOS�i�������|�l��

27.4�i����������

27.5D�|�l���������C��

���Y

�īI���x

����

��28�����B��ͬ������

28.1ͬ������

28.2�����B

28.3�M�벢�����ڷǷ���B�Ŀ�����

28.4�����B����C

���Y

�īI���x

����

��29��ͬ�������OӋ

29.1ͬ��������;

29.2����ͬ����

29.3�������̖���}

29.4FIFOͬ����

���Y

�īI���x

����

���VHDL���a�L����Z��ָ��

���AVHDL���a�L��

���BVHDL�Z��ָ��

�����īI

��������c늚�̼��g���������·�OӋ�̳�:VHDLϵ�y���F/WILLIAM JAMES DALLY ���ߺ���

William J. Dally ˹̹����W����ϵWillard R.��Inez Kerr Bell���ڡ�NVIDIA��˾��ϯ�ƌW�ҡ��������ҹ���ԺԺʿ��IEEE/ACM/����ˇ�g�c�ƌW�WԺ���T�����@�����S���s�u������ACM Eckert-Mauchly����IEEE Seymour Cray����ACM Maurice Wilkes���� R. Curtis Harting �ȸ��ܛ�����̎�������˹̹����W��ʿ�Wλ������2007�ꮅ�I�ڶſ˴�W�@�ÌWʿ�Wλ������늚��cӋ��C���̺�Ӌ��C�ƌW����2009�꣬����˹̹����W�@�ôTʿ�Wλ�� Tor M. Aamodt ����炐�ȁ���W늚��cӋ��C����ϵ�����ڡ����c�о���һ���_�l��GPGPU-Simģ�M����������ƪ�P��ͨ��GPU�Y����Փ���ѱ��x������IEEE�s־�ġ����T���x����һƪ��������Ӌ��C�f����ACM���s־ͨ�ŷ���ġ��о����c������2012 - 2013����ݼ����g����˹̹����WӋ��C�ƌWϵ���������ڣ���2004����2006�꣬����NVIDIA��˾�������о�GeForce 8ϵ��GPU�ăȴ�ϵ�y�ܘ����������_��������

- >

�S�@ʳ��

- >

����Ԣ��-�����ČW�������-ȫ�g��

- >

�ҏ�δ��˾�����g

- >

���ČW���ɾ���--��Ѹ�c���m/�t�T�W�g����(�t�T�W�g����)

- >

���Ҏ����x��Ѹ:�����¾�

- >

���������~����Փ/���С��

- >

�����b�L�������o���ӵ��Ї���Ԓ

- >

ɽ����

![�]�������đ������P����؛���c�Q��](http://image31.bookschina.com/pro-images/250513gs/487100.jpg?id=81)